|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

| СПОСОБ ВЫПОЛНЕНИЯ ОПЕРАЦИЙ СЧИТЫВАНИЯ В МУЛЬТИПРОЦЕССОРНОЙ КОМПЬЮТЕРНОЙ СИСТЕМЕ |  |

Номер публикации патента: 2183850 |  |

| Редакция МПК: | 7 | | Основные коды МПК: | G06F012/08 | | Аналоги изобретения: | AL-SADOUN Н. В. ЕТ AL. CACHE COHERENCY IN MULTIPLE BUS SYSTEM" INTERNATIONAL JOURNAL OF ELECTRONICS. Vol. 73, no.3, 1 September 1992. JP 8328957 A2, 13.12.1996. RU 2010317, 30.03.1994. RU 2060538 C1, 20.05.1996. |

| Имя заявителя: | ИНТЕРНЭШНЛ БИЗНЕС МАШИНЗ КОРПОРЕЙШН (US) | | Изобретатели: | АРИМИЛЛИ Рави Кумар (US)

ДОДСОН Джон Стивен (US)

КЕЙЗЕР Джон Майкл (US)

ЛУИС Джерри Дон (US) | | Патентообладатели: | ИНТЕРНЭШНЛ БИЗНЕС МАШИНЗ КОРПОРЕЙШН (US) | | Номер конвенционной заявки: | 08/837,516 | | Страна приоритета: | US | | Патентный поверенный: | Веселицкая Ирина Александровна |

Реферат |  |

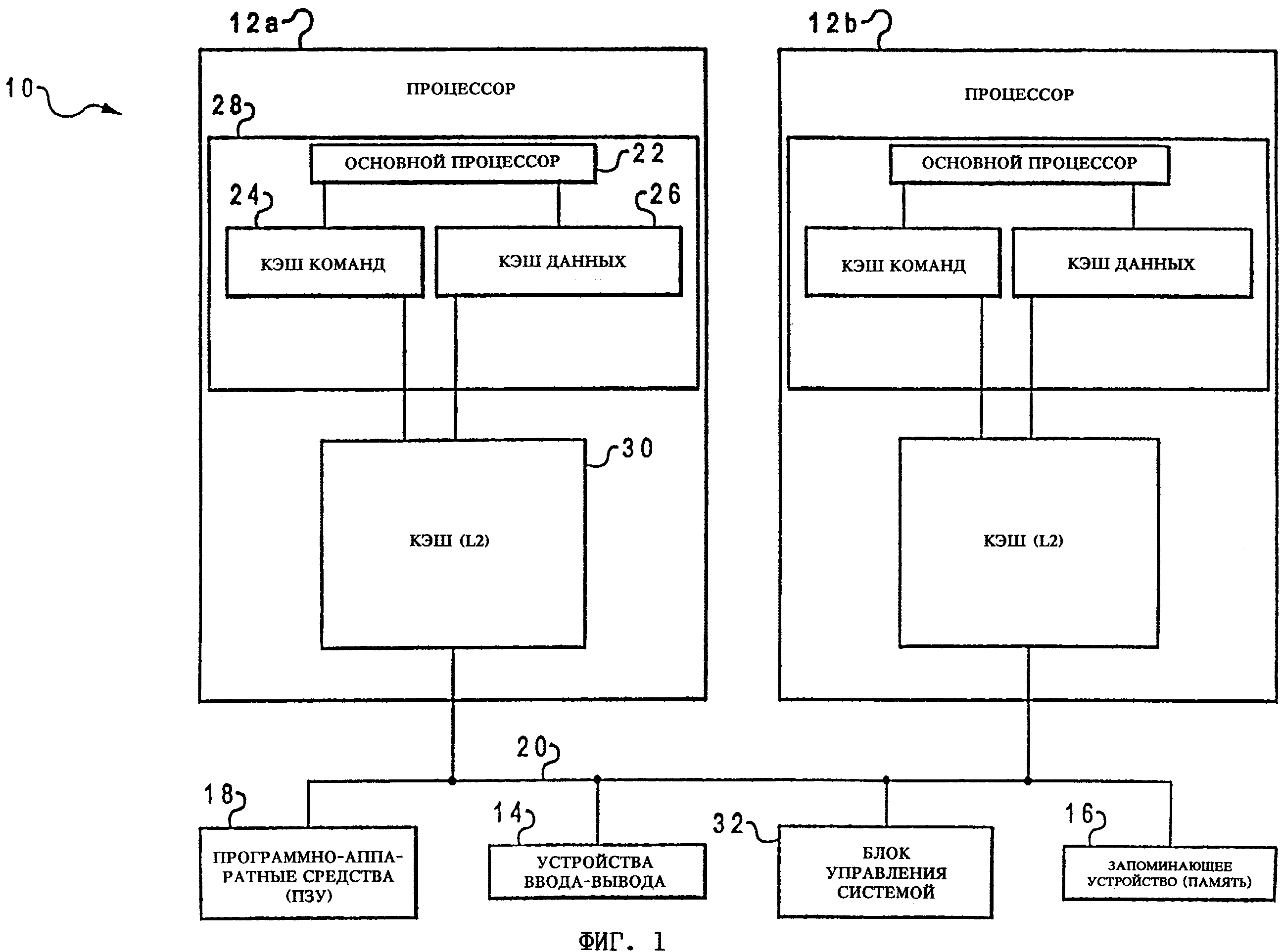

Изобретение относится к компьютерным системам, в частности к способу выполнения операций считывания из памяти в симметричных мультипроцессорных компьютерных системах. Техническим результатом изобретения является разработка усовершенствованного способа выполнения операций считывания в мультипроцессорной компьютерной системе. Предложено после загрузки информации из системной памяти по крайней мере в два кэша последние маркировать как содержащие совместные неизмененные копии информации, и, когда запрашивающий процессор посылает сообщение, показывающее, что он хочет считать информацию, один определенный кэш выдает ответ, указывающий на то, что он является источником информации. Этот ответ передается кэшу, извлекающему сообщения из схемы внутренних соединений, которая соединена с запрашивающим процессором. Ответ обнаруживается системной логикой и направляется из нее в запрашивающий процессор. Кэш затем выдает информацию в схему внутренних соединений, которая соединена с запрашивающим процессором. Системная память обнаруживает сообщение и в норме служит источником информации, при этом, однако, ответ информирует запоминающее устройство системы также о том, что вместо него источником информации служит кэш. Поскольку запаздывание в сверхоперативной памяти можно сделать меньшим запаздывания в системной памяти, то использование такого нового протокола позволяет существенно улучшить эффективность считывания. 4 с. и 30 з.п.ф-лы, 3 ил., 3 табл.

|