|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N • N) - МАТРИЦЫ |  |

Номер публикации патента: 2073382 |  |

| Имя заявителя: | Якуш Виктор Павлович[RU] | | Изобретатели: | Якуш Виктор Павлович[RU]

Драницин Олег Николаевич[RU]

Лиходед Николай Александрович[BY]

Соболевский Павел Иосифович[BY]

Тиунчик Александр Александрович[BY] | | Патентообладатели: | Якуш Виктор Павлович[RU]

Драницин Олег Николаевич[RU]

Лиходед Николай Александрович[BY]

Соболевский Павел Иосифович[BY]

Тиунчик Александр Александрович |

Реферат |  |

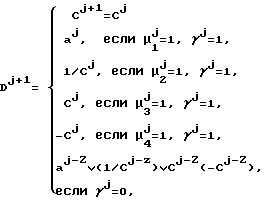

1. Устройство для вычисления собственных значений (n x n) - матрицы, содержащее вычислительный модуль первого типа, l вычислительных модулей второго типа (1 < 2n) и блок анализа, причем i-й вход группы информационных входов и i-й вход первой группы управляющих входов  устройства подключены соответственно к первому информационному входу и первому управляющему входу i-го вычислительного модуля второго типа, первый информационный вход, первый и второй управляющие входы устройства подключены соответственно к первому информационному входу, первому и второму управляющим входам вычислительного модуля первого типа, первый информационный выход вычислительного модуля первого типа подключен к второму информационному входу первого вычислительного модуля второго типа, первый информационный выход i-го вычислительного модуля второго типа устройства подключены соответственно к первому информационному входу и первому управляющему входу i-го вычислительного модуля второго типа, первый информационный вход, первый и второй управляющие входы устройства подключены соответственно к первому информационному входу, первому и второму управляющим входам вычислительного модуля первого типа, первый информационный выход вычислительного модуля первого типа подключен к второму информационному входу первого вычислительного модуля второго типа, первый информационный выход i-го вычислительного модуля второго типа  подключен к второму информационному входу (i + 1)-го вычислительного модуля второго типа, третий информационный вход i-го вычислительного модуля второго типа подключен к второму информационному входу (i + 1)-го вычислительного модуля второго типа, третий информационный вход i-го вычислительного модуля второго типа  подключен к второму информационному выходу (i + 1)-го вычислительного модуля второго типа, второй информационный выход первого вычислительного модуля второго типа подключен к второму информационному входу вычислительного модуля первого типа, второй информационный выход которого подключен к первому информационному входу блока анализа, второй информационный вход которого подключен к входу задания точности вычислений устройства, синхровход которого подключен к синхровходам всех вычислительных модулей и блока анализа, i-й выход группы выходов блока анализа подключен к второму информационному выходу (i + 1)-го вычислительного модуля второго типа, второй информационный выход первого вычислительного модуля второго типа подключен к второму информационному входу вычислительного модуля первого типа, второй информационный выход которого подключен к первому информационному входу блока анализа, второй информационный вход которого подключен к входу задания точности вычислений устройства, синхровход которого подключен к синхровходам всех вычислительных модулей и блока анализа, i-й выход группы выходов блока анализа  подключен к i-му выходу группы выходов устройства, информационный выход которого подключен к выходу признака окончания вычислений устройства, отличающееся тем, что i-й вход второй группы управляющих входов подключен к i-му выходу группы выходов устройства, информационный выход которого подключен к выходу признака окончания вычислений устройства, отличающееся тем, что i-й вход второй группы управляющих входов  устройства подключен к второму управляющему входу i-го вычислительного модуля второго типа, третий управляющий вход устройства подключен к третьему управляющему входу вычислительного модуля первого типа, первый и второй управляющие выходы вычислительного модуля первого типа подключены соответственно к третьему и четвертому управляющим входам первого вычислительного модуля второго типа, первый и второй управляющие выходы i-го вычислительного модуля второго типа устройства подключен к второму управляющему входу i-го вычислительного модуля второго типа, третий управляющий вход устройства подключен к третьему управляющему входу вычислительного модуля первого типа, первый и второй управляющие выходы вычислительного модуля первого типа подключены соответственно к третьему и четвертому управляющим входам первого вычислительного модуля второго типа, первый и второй управляющие выходы i-го вычислительного модуля второго типа  подключены соответственно к третьему и четвертому управляющим входам (i + 1)-го вычислительного модуля второго типа, причем вычислительный модуль первого типа выполнен с возможностью реализации следующих функций: подключены соответственно к третьему и четвертому управляющим входам (i + 1)-го вычислительного модуля второго типа, причем вычислительный модуль первого типа выполнен с возможностью реализации следующих функций:

где αj и βj - значения соответственно на первом и втором управляющих входах вычислительного модуля на j-м такте;

Aj+1 и Bj+1 - значения соответственно на первом и втором управляющих выходах вычислительного модуля на (j+1)-м такте;

где aj и Cj - значения соответственно на первом и втором информационных входах вычислительного модуля на j-м такте;

Dj+1 и Cj+1 - значения соответственно на первом и втором информационных выходах вычислительного модуля на (j+1)-м такте;

γj - значения на третьем управляющем входе вычислительного модуля на j-м такте,

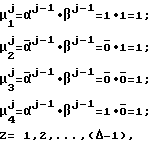

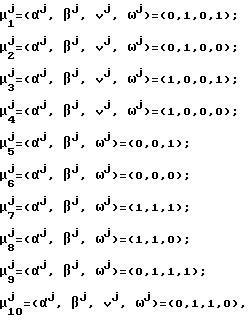

а вычислительный модуль второго типа выполнен с возможностью реализации следующих функций:

где αj и βj- значения соответственно на третьем и четвертом управляющих входах вычислительного модуля на j-м такте,

Aj+&Dgr; и βj+&Dgr;- значения соответственно на первом и втором управляющих выходах вычислительного модуля на (j+&Dgr;)-м такте;

где Cj - значение на втором информационном входе вычислительного модуля на j-м такте;

Cj+&Dgr; - значение на первом информационном выходе вычислительного модуля на (j+&Dgr;)-м такте;

где aj и bj - значения соответственно на первом и третьем информационных входах вычислительного модуля на j-м такте;

Fj+n&Dgr;-1- значения на втором информационном выходе вычислительного модуля на (j+n&Dgr;-1)-м такте;

где vj и ωj - значения соответственно на первом и втором управляющих входах вычислительного модуля на j-м такте,

μj@1÷ μj@10 - значения соответственно на выходах с первого по десятый блока управления вычислительного модуля на j-м такте. 2. Устройство по п. 1, отличающееся тем, что блок анализа содержит 2n регистров, n вычитателей, n схем сравнения, делитель с модулем счета (&Dgr;n+n), делитель с модулем счета &Dgr;·n2 триггер, три элемента И и элемент ИЛИ, причем в блоке анализа первый информационный вход блока анализа подключен к информационному входу первого регистра, выход i-го регистра  подключен к информационному входу (i + 1)-го регистра, к i-му выходу группы выходов блока анализа и первому входу i-го вычитателя, второй вход которого подключен к выходу (i + n)-го регистра, выход i-го вычитателя подключен к информационному входу (i + 1)-го регистра, к i-му выходу группы выходов блока анализа и первому входу i-го вычитателя, второй вход которого подключен к выходу (i + n)-го регистра, выход i-го вычитателя  подключен к первому входу i-й схемы сравнения, вторые входы схем сравнения объединены и являются вторым информационным входом блока анализа, выход i-й схемы сравнения подключен к первому входу i-й схемы сравнения, вторые входы схем сравнения объединены и являются вторым информационным входом блока анализа, выход i-й схемы сравнения  подключен к i-му входу первого элемента И, выход которого подключен к выходу признака окончания вычисления блока анализа, синхровход которого подключен к первым входам второго и третьего элементов И и счетным входам делителей с модулями счета (&Dgr;n+n) и (&Dgr;n2), выход делителя с модулем счета (&Dgr;n2) подключен к информационному входу триггера, выход которого подключен к второму входу второго элемента И и входу установки в нулевое состояние делителя с модулем счета (&Dgr;n+n), выход которого и выход второго элемента И подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к второму входу третьего элемента И, выход которого подключен к синхровходам всех регистров. подключен к i-му входу первого элемента И, выход которого подключен к выходу признака окончания вычисления блока анализа, синхровход которого подключен к первым входам второго и третьего элементов И и счетным входам делителей с модулями счета (&Dgr;n+n) и (&Dgr;n2), выход делителя с модулем счета (&Dgr;n2) подключен к информационному входу триггера, выход которого подключен к второму входу второго элемента И и входу установки в нулевое состояние делителя с модулем счета (&Dgr;n+n), выход которого и выход второго элемента И подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к второму входу третьего элемента И, выход которого подключен к синхровходам всех регистров.

|