|

На данной странице представлена ознакомительная часть выбранного Вами патента

Для получения более подробной информации о патенте (полное описание, формула изобретения и т.д.) Вам необходимо сделать заказ. Нажмите на «Корзину»

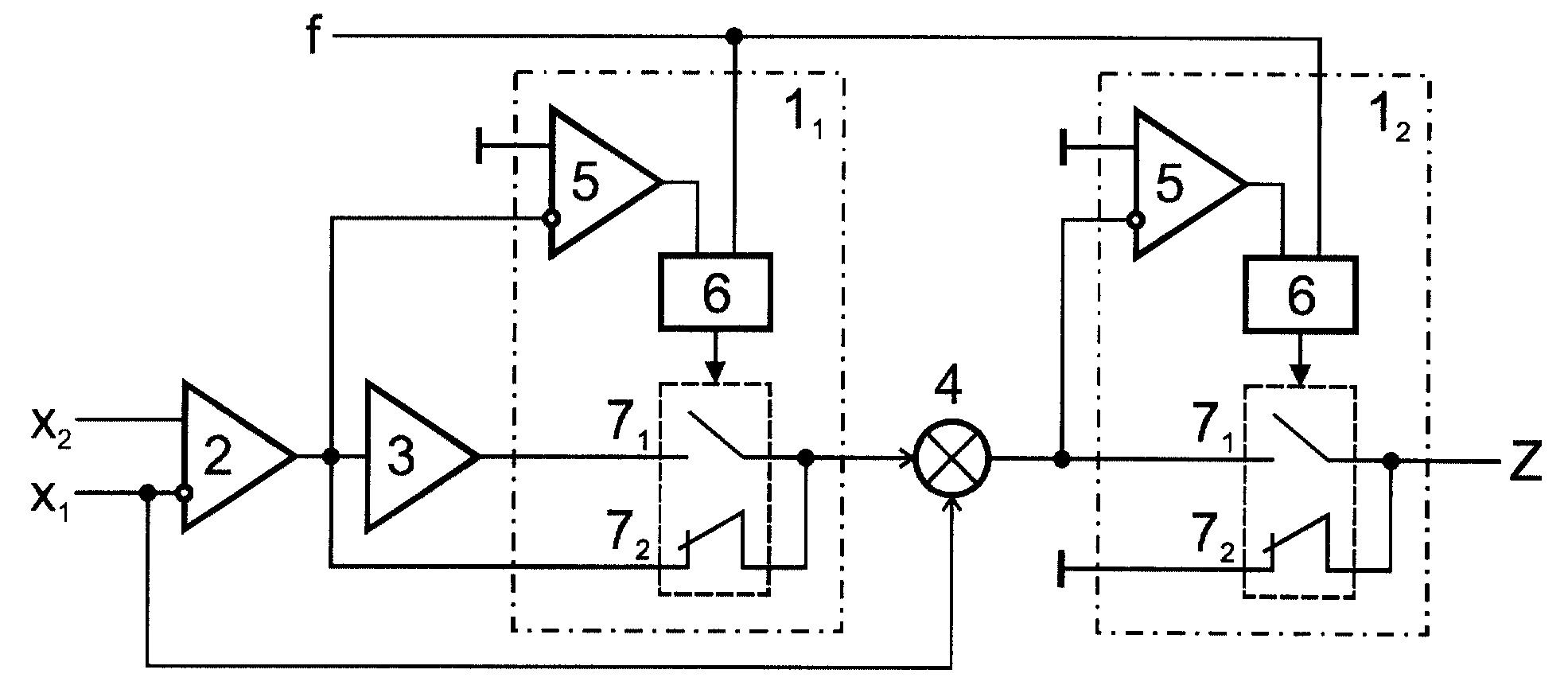

| ПАРИТЕТНЫЙ РАСПОЗНАВАТЕЛЬ |  |

Номер публикации патента: 2176103 |  |

| Редакция МПК: | 7 | | Основные коды МПК: | G06G007/25 H03K005/24 | | Аналоги изобретения: | RU 2143733 C1, 27.12.1999. RU 2137191 C1, 10.09.1999. SU 1251114 A, 15.08.1986. RU 2117329 C1, 10.08.1998. RU 2112276 C1, 27.05.1998. US 5381054 A, 10.01.1995. Электронное моделирование, 1998, № 2, с.12, рис.5г. |

| Имя заявителя: | Ульяновский государственный технический университет | | Изобретатели: | Андреев Д.В. | | Патентообладатели: | Ульяновский государственный технический университет |

Реферат |  |

Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, аналоговых процессоров и др. Паритетный распознаватель содержит инвертор знака (3) и первый релятор, который состоит из компаратора (5), подключенного выходом к первому входу булевого элемента "исключающее ИЛИ" (6), второй вход которого является входом управления первого релятора, а выход соединен с управляющим входом замыкающего и размыкающего ключей компаратора (7), выходы которых объединены и образуют выход первого релятора. Первый, второй и третий, четвертый входы первого релятора подключены соответственно к неинвертирующему, инвертирующему входам компаратора (5) и входу замыкающего, входу размыкающего компаратора (7). Первый вход первого релятора заземлен, а третий и объединенные второй, четвертый входы соединены соответственно с выходом и входом инвертора знака (3). Введены аналогичный первому второй релятор, дифференциальный усилитель (2) и сумматор (4). Выход и инвертирующий вход дифференциального усилителя (2) соединены соответственно с входом инвертора знака (3) и вторым входом сумматора (4), подключенного первым входом и выходом соответственно к выходу первого релятора и объединенным второму, третьему входам второго релятора, первый и четвертый входы которого заземлены. Выход и вход управления второго релятора, подключенный к входу управления первого релятора, являются соответственно выходом и управляющим входом паритетного распознавателя, первый и второй информационные входы которого образованы соответственно инвертирующим и неинвертирующим входами дифференциального усилителя (2). Технический результат: расширение функциональных возможностей за счет обеспечения идентификации равенства двух изменяющихся во времени аналоговых сигналов. 1 ил.

|